ELECTRONICS-DSC -1005 D Semester: IV Electronics-Paper- IV Advance Communication and Microcontroller 8051 Section II: Microcontroller 8051

**Unit 2: Instruction Set of 8051**

Classification of instruction sets, Addressing modes .

Instruction set of 8051: data transfer, arithmetic, Logical, Jump, call,

Boolean instructions.

### Addressing modes:-

The ways to specify the address of data in instruction is called addressing modes. The data could be in a register, or in memory, or be provided as an immediate value. There are four addressing modes.

1) Immediate addressing mode

2) Direct addressing mode

3) Register addressing modes

4) Indirect addressing modes (indirect register addressing mode)

5) Indexed addressing mode

#### Immediate addressing mode:-

In this instruction data is directly written in the instruction. i.e. data is a part of instruction. 1)MOV A, #data (MOV A, #55)  $\rightarrow$  copy specified data into accumulator. 2)MOV Rn, #data(MOV R0,#22H) $\rightarrow$ copy specified data into Register(R0-R7). 3) ADD A, # data $\rightarrow$  Adds the specified data with content of accumulator. 4)SUBB A, #data $\rightarrow$  Subtract the specified data with the content of accumulator. 5)ORL A, #data $\rightarrow$  The specified data is ORed with the content of accumulator. 6)MOV DPTR,#16bit data  $\rightarrow$  Copy the 16-bit data into DPTR. e.g. MOV DPTR, #9006.

#### **Direct Addressing mode:-**

All 128 bytes of internal RAM & SFR`S can be addressed using assigned values. In this instruction, the address of operands are directly specified.

1)MOVA, add  $\rightarrow$  Copy data from location specified by given address into Accumulator.

| A)MOV A, 80H                                  | ;Read the content of port P0(add 80H) & copy them into Acc. |

|-----------------------------------------------|-------------------------------------------------------------|

| B)MOV 80H, A                                  | ;write into port P0.                                        |

| C)MOV PSW, A (move ]                          | D0,E0); Move the content of Acc. Into flags.                |

| 2)MOV Rn, add $\rightarrow$ Copy data from lo | ocations specified by given address into register Rn.       |

| e.g.MOV R2,12H                                | ; copy data from location specified by 12h into R2.         |

3)Add Address  $\rightarrow$  Adds the data from the location specified by given address with the content of accumulator.

4)XCH A, Address  $\rightarrow$  Exchange the data from the location specified by given address with the content of accumulator. 5)XRL A, address  $\rightarrow$  The data from the location specified by given address is XORed with the content of accumulator.

#### **Register Addressing mode:-**

In register addressing mode, the register A(accumulator), R0-R7 are specified in the instruction itself. (R0-R7) are used in currently selected bank.

e.g. 1)MOV A, R0; Move data from register R0 to A A←R If R0=55H then A=55H

2)MOV A, Rn ; A←Rn.

3)ADD A, Rn ; Adds the content of register Rn with Accumulator.

4)SUBB A, Rn; Subtracts the contents of register Rn from Acc with Borrow.

5)XRL A, Rn ; The contents of register Rn are XOred with accumulator content.

6)XCH A, Rn ; The content of register Rn & Acc are exchanged.

7)ANL A, Rn ; The content of register Rn are ANDed with accumulator.

8)ADDC A, Rn; The content of Rn are added into Accumulator with carry movement of data between register. Rn is not allowed i.e. MOV R5, R6 is not valid (only R0,R1 are used as pointer

register)

#### Indirect (Register)addressing mode:-

In this addressing mode, register is used to hold the actual address of operand or data. The register itself is not the address. These instructions uses R0, R1 as data pointer and register, but R2-R7 are not allowed to hold address.

1)MOV A, @Ro ; Move to accumulator content of memory location pointed by reg. R0

2)MOV @R1, A; move the content of the accumulator into memory location pointed by register R1.

3)ADD A,@R0; Adds the content of memory location pointed b register R0 with content of accumulator

4)SUB A,@R1; Subtracts the content of memory location pointed out by register R1 from contents of accumulator.

5)INC @R0; increment the contents of memory location pointed out by register R0.

6)DEC @R1;Decrement the contents of memory location pointed by regsiter.

7)ANL A,@R; The content of memory location pointed out by reg R1 is ANDed with content of accumulator. But, MOV A,@R3;This is not valid.

#### Indexed addressing mode( External addressing mode):-

It is widely used in accessing data elements of look-up table entries located in the program ROM.

•MOVC A,@A+DPTR : Here MOVC, "C" means code. The contents of A are added to the 16-bit register DPTR to form the 16-bit address from which data is copied into A.

•MOVC A,@A+PC : The contents of A are added to the 16-bit register PC to form the 16-bit address from which data is copied into A.

## **2.1 Addressing modes**

When controller executes an instruction, it perform the specific function on data. The different ways to specify the address of data in an instruction are called as addressing modes.

## **2.1.1 Types of Addressing Modes**

- •Direct addressing mode

- •Register Indirect addressing mode

- •Register addressing mode

- •Immediate addressing mode

- •Indexed / External addressing mode

## •Direct addressing mode

In this mode the operand is specified by an 8 bit address field in the instruction .Internal RAM and all SFRs can be accessed by direct addressing mode. The internal memory address from 00H to 7FH and the SFRs can access from 80H to FFH

e.g. MOV A, 60H ; copy the content of memory location 60H to register A

### •Register Indirect addressing mode

In this addressing mode, the instruction specifies the register which contains the address of an operand. The registers from the register bank are used as a memory pointer. The @ sign indicated the register acts as a pointer to memory location. Only R0 and R1 registers are used as pointers for selected bank.

e.g. **MOV** A,@R0 ; copy the content of the memory location whose address id pointed by register R0

• Register addressing mode

In this addressing mode the operand is copied from one register to another register. In this addressing mode both source and destination are registers.

e.g. MOV A, R0 ; copy the content of R0 to register A

## •Immediate addressing mode

This method is the simplest method to transfer a data. In this addressing mode the operand/data is the part of instruction. The # sign indicates that the data followed immediate by operand.

e.g. MOV A,#20H ; copy the immediate data to register A

## Indexed/External addressing mode

Using this addressing mode only external program memory can be accessed. This addressing mode is used to read the lookup table. Either the DPTR or PC is used as a memory pointer.

e.g. MOVC A,@A+DPTR ; copy the content of memory location to register A pointed by DPTR register

The 8051 instruction set is divided into different groups

- 1. Data Transfer Instructions

- 2. Arithmetic Instructions

- 3. Logical Instructions

- 4. Bit Processing Instructions

- 5. Program Branching Instructions

# **1. Data Transfer Instructions**

### 2.2 Data Transfer Instructions

The microcontroller spends its most of the time in coping the data one to another. So 8051 instruction set is full of data movement instruction

| Mnemonic      | Operation              | Addressing<br>mode | Number of<br>bytes | Example     | Description                                                                                                       |

|---------------|------------------------|--------------------|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| MOV A ,Rn     | Rn A                   | Register           | 1                  | MOV A ,R1   | Copy the data from R1 of the selected register bank and store it to register A                                    |

| MOV A ,direct | Addr 🛶 A               | Direct             | 2                  | MOV A , 60H | Copy the data from specified address i.e.<br>60H and store it to register A                                       |

| MOV A ,@Rn    | Addr(Rn)→ A            | Indirect           | 1                  | MOV A ,@R1  | Copy the data from the address specified<br>within R1 of the selected register bank<br>and store it to register A |

| MOV A ,#data  | Data <del>&gt;</del> A | Immediate          | 2                  | MOV A ,#30H | Copy the data immediate data specified within instruction to register A                                           |

| MOV Rn ,A     | A → Rn                 | Register           | 1                  | MOV R7 ,A   | Copy the data from register A to register<br>R7 of the selected register bank                                     |

| MOV Rn,direct | Addr → Rn              | Direct             | 2                  | MOV R1,30H  | Copy the data from specified address i.e.<br>30H and store it to R1 of the selected<br>register bank              |

| MOV Rn,#data  | Data → Rn              | Immediate          | 1                  | MOV R5,#20H | Copy the data immediate data specified<br>within instruction to register R5 of the<br>selected register bank      |

| MOV direct ,A         | A → addr                                                        | Direct               | 2 | MOV 70H ,A     | Copy the content of the register A to the<br>address specified within the instruction<br>i.e. 70H                                      |

|-----------------------|-----------------------------------------------------------------|----------------------|---|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| MOV direct,Rn         | Addr → Rn                                                       | Direct               | 2 | MOV 30H,R2     | Copy the content of the register R2 of<br>the selected register bank to the address<br>specified within the instruction i.e. 30H       |

| MOV<br>direct,direct  | Addr → Addr                                                     | Direct               | 3 | MOV 30H,60H    | Copy the content of the memory location<br>60H to the memory address 30H                                                               |

| MOV direct<br>,@Rn    | Addr(Rn)→ addr                                                  | Register<br>indirect | 2 | MOV 30H ,@R0   | Copy the content of the memory<br>addresses specified in the register R0 of<br>the selected register bank to the memory<br>address 30H |

| MOV direct ,#<br>data | Data → addr                                                     | Immediate            | 3 | MOV 20H ,# 30H | Copy the immediate data 30H to the<br>memory address 20H                                                                               |

| MOV @Rn,A             | $\begin{array}{c} A \longrightarrow & Addr \\ (Rn) \end{array}$ | Register             | 1 | MOV @R3,A      | Copy the content of register A to the addresses specified within R3 of the selected register bank.                                     |

| MOV @Rn,direct        | Direct→ Addr<br>(Rn)                                            | Direct               | 2 | MOV @R7,30H    | Copy the content of memory location<br>30H to the address specified within R7 of<br>the selected register bank.                        |

| MOV@Rn,#data                | Data <b>→</b> addr                                              | Immediate | 2 | MOV @R5,#40H       | Copy the immediate data to the memory<br>location specified within register R5 of<br>the selected register bank.                 |

|-----------------------------|-----------------------------------------------------------------|-----------|---|--------------------|----------------------------------------------------------------------------------------------------------------------------------|

| MOV<br>DPTR,#data 16<br>bit | Data → DPTR                                                     | Immediate | 3 | MOV<br>DPTR,#7000H | Copy the immediate data to the 7000h to the DPTR                                                                                 |

| MOVC<br>A,@A+DPTR           | $(A+DPTR) \longrightarrow A$                                    | Indirect  | 1 | MOVC<br>A,@A+DPTR  | Add the content of the register A and<br>DPTR to generate address. copy the<br>content of generated address to the<br>register A |

| MOVX<br>A,@DPTR             | addr (DPTR)→ A                                                  | Indirect  | 1 | MOVX<br>A,@DPTR    | Copy the content of the address specified within DPTR to the register A                                                          |

| MOVX<br>@DPTR,A             | $\begin{array}{c} A \longrightarrow addr \\ (DPTR) \end{array}$ | Indirect  | 1 | MOVX<br>@DPTR,A    | Copy the content of register A to the<br>address specified in DPTR                                                               |

| MOVX @Rn,A                  | A → addr (Rn)                                                   | Indirect  | 1 | MOVX @R0,A         | Copy the content of register A to the<br>address specified in R0 of the selected<br>register bank                                |

| PUSH direct                 | $addr \rightarrow SP$<br>SP=SP+1                                | Direct    | 2 | PUSH DPH           | Copy the content of DPTR higher byte to<br>the memory location pointed by the stack<br>pointer                                   |

| POP direct                  | SP → Direct                                                     | Direct    | 2 | POP DPH            | Copy the content of the memory location<br>pointed by stack pointer to DPTR higher<br>byte                                       |

| XCH A ,Rn     | A <del>₹</del> Rn   | Register             | 1 | XCH A,R5    | Exchange the data between register A<br>and register R5 of the selected register<br>bank                                      |

|---------------|---------------------|----------------------|---|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| XCH A ,direct | addr 컱 🛛 Rn         | Direct               | 2 | XCH A,50H   | Exchange the data between register A<br>and the specified address within the<br>instruction i.e. 50H                          |

| XCH A ,@Rn    | A <b>₹</b> addr(Rn) | Register<br>indirect | 1 | XCH A,@R5H  | Exchange the <u>data</u> between register A<br>and the address specified within R5<br>register of the selected register bank. |

| XCHD A ,@Rn   | A(3-0)              | Register<br>indirect | 1 | XCHD A,@R5H | Exchange the lower nibble of data<br>between register A and the address<br>specified within R5 register of                    |

# **2. Arithmetic Instructions**

| Mnemonic          | Operation                         | Addressing<br>mode | Number<br>of Bytes | Example    | Description                                                                                                                                                                                |

|-------------------|-----------------------------------|--------------------|--------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD A,Rn          | A+Rn $\longrightarrow$ A          | Register           | 1                  | ADD A,R5   | The content of register A added with content of register R5 of the selected register bank and result is stored in register A                                                               |

| ADD A, direct     | $A+addr \longrightarrow A$        | Direct             | 2                  | ADD A,20H  | The content of register A is added with content<br>of memory location specified within instruction<br>i.e. 20H and result is stored in register A                                          |

| ADD A, @Rn        | A+ addr(Rn) $\longrightarrow$ A   | indirect           | 1                  | ADD A,@R0  | The content of register A is added with content<br>of memory location specified within register R0<br>of the selected register bank and result is<br>stored in register A                  |

| ADD A, #data      | A+ data → A                       | Immediate          | 2                  | ADD A,#30H | The content of register A is added with immediate data and result is stored in register A                                                                                                  |

| ADDC A,Rn         | A+Rn+CY → A                       | Register           | 1                  | ADDC A,R5  | The content of register A is added with content<br>of register $R5$ of the selected register bank<br>and a carry bit. The result is stored in register<br>A                                |

| ADDC A,<br>direct | A+ addr+CY $\longrightarrow$ A    | Direct             | 2                  | ADDC A,20H | The content of register A is added with content<br>of memory location specified within instruction<br>i.e. 20H and a carry bit. The result is stored in<br>register A                      |

| ADDC A,<br>@Rn    | $A+addr(Rn)+CY \longrightarrow A$ | indirect           | 1                  | ADDC A,@R0 | The content of register A is added with content<br>of memory location specified within register R0<br>of the selected register bank and a carry bit.<br>The result is stored in register A |

| + | Į              |                       |                    |                    |             | I                                                                                                                                                                               |

|---|----------------|-----------------------|--------------------|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Mnemonic       | Operation             | Addressing<br>mode | Number<br>of Bytes | Example     | Description                                                                                                                                                                     |

|   | SUBB A, Rn     | A-Rn-CY → A           | Register           | 1                  | SUBB A,R5   | The content of register <u>R5</u> and a carry flag are<br>subtracted from the content of register A. The<br>result is stored in register A                                      |

|   | SUBB A, direct | A- addr-CY → A        | Direct             | 2                  | SUBB A,20H  | The content of memory location and a carry<br>flag are subtracted from the content of register<br>A. The result is stored in register A                                         |

|   | SUBB A, @Rn    | A-addr(Rn)-CY → A     | Indirect           | 1                  | SUBB A,@R0  | The content of memory location whose address<br>is stored in <u>R0</u> and a carry flag are subtracted<br>from the content of register A. The result is<br>stored in register A |

|   | SUBB A, #data  | A- data-CY <b>→</b> A | Immediate          | 2                  | SUBB A,#30H | The immediate data and a carry flag are<br>subtracted from the content of register A. The<br>result is stored in register A                                                     |

2.3.3. Increment : The increment is performed using instruction INC. The operand value is incremented by one. flags are not affected upon the execution of these instructions.

| Mnemonic   | Operation                         | Addressing<br>mode | Number<br>of Bytes | Example  | Description                                                                           |

|------------|-----------------------------------|--------------------|--------------------|----------|---------------------------------------------------------------------------------------|

| INC Rn     | Rn+1 → Rn                         | Register           | 1                  | INC R6   | The content of register R6 is incremented by one                                      |

| INC direct | $addr + 1 \rightarrow addr$       | Direct             | 2                  | INC 30H  | The content of memory location is<br>incremented by one                               |

| INC @Rn    | $addr(Rn)+1 \rightarrow addr(Rn)$ | Indirect           | 1                  | INC @R0  | The content of memory location whose address<br>is stored in R0 is incremented by one |

| INC DPTR   | DPTR+1 -> DPTR                    | Register           | 1                  | INC DPTR | The content of register DPTR is incremented<br>by one                                 |

**2.3.4.** Decrement : The decrement is performed using instruction DEC. The operand value is incremented by one. flags are not affected upon the execution of these instructions.

| Mnemonic   | Operation                         | Addressing<br>mode | Number<br>of Bytes | Example  | Description                                                                           |

|------------|-----------------------------------|--------------------|--------------------|----------|---------------------------------------------------------------------------------------|

| DEC Rn     | Rn-1 🛶 Rn                         | Register           | 1                  | DEC R6   | The content of register R6 is decremented by one                                      |

| DEC direct | addr -1 🛶 addr                    | Direct             | 2                  | DEC 30H  | The content of memory location is decremented by one                                  |

| DEC @Rn    | $addr(Rn)-1 \rightarrow addr(Rn)$ | Indirect           | 1                  | DEC @R0  | The content of memory location whose address<br>is stored in R0 is decremented by one |

| DEC DPTR   | DPTR-1 -> DPTR                    | Register           | 1                  | DEC DPTR | The content of register DPTR is decremented by one                                    |

#### 2.3.5. Multiplication:

The 8051 microcontroller has a capability of 8 bit multiplication using register A and B. For multiplication register A and B act as source as well as destination. In 8 bit multiplication 16 bit result is generated. The higher byte is stored in register B and lower byte is stored in register A. The over flow flag (OV) flag is set if result of the grater than FFh.

| Mnemonic | Operation          | Addressing<br>mode | Number<br>of Bytes | Example | Description                                                                                             |

|----------|--------------------|--------------------|--------------------|---------|---------------------------------------------------------------------------------------------------------|

| MUL AB   | AXB → A(0-7)B(0-7) | Register           | 1                  | MUL AB  | The content with in register A and B are<br>multiplied ad the result is stored in A and B<br>registers. |

#### 2.3.6. Division :

8051 microcontroller can perform 8 bit division. the content of register A is divided by the content of register B. After division quotient is stored in register A and remainder stored in register B. over flow (OV) flag is set if the content is divided by zero.

| Mnemonic | Operation                                                | Addressing<br>mode | Number<br>of Bytes | Example | Description                                                                                                         |

|----------|----------------------------------------------------------|--------------------|--------------------|---------|---------------------------------------------------------------------------------------------------------------------|

| DIV AB   | $A \div B \longrightarrow A(quotient)$<br>B (remainder ) | Register           | 1                  | DIV AB  | The content of register A is divided by content<br>of register B. and the result is stored in A and<br>B registers. |

2.3.7. Decimal Arithmetic:

8051 can perform the BCD arithmetic addition. Using DA A instruction the result within register A is converted into BCD numbers.

| Mnemonic | Operation                  | Addressing<br>mode   | Number<br>of Bytes | Example | Description                                                           |

|----------|----------------------------|----------------------|--------------------|---------|-----------------------------------------------------------------------|

| DA A     | $A \longrightarrow A(BCD)$ | Register<br>specific | 1                  | DA A    | The content of register A is converted into<br>equivalent BCD numbers |

# **3. Logical Instructions :**

| Mnemonic            | Operation                         | Addressing<br>mode | Number<br>of Bytes | Example      | Description                                                                                                                                        |

|---------------------|-----------------------------------|--------------------|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| ANL A, Rn           | A( <u>ANDed)Rn</u> → A            | Register           | 1                  | ANL A, R4    | The content of register R4 is ANDed with the<br>content of register A. The result is stored in<br>register A                                       |

| ANL A, direct       | A( <u>ANDed)addr</u> → A          | Direct             | 2                  | ANL A, 20H   | The content of memory location 20H ANDed<br>with content of register A. The result is<br>stored in register A                                      |

| ANL A,@Rn           | A (ANDed)addr(Rn) $\rightarrow$ A | Indirect           | 1                  | ANL A, @R5   | The content of memory location whose address<br>is stored in R5 <u>ANDed with the content of</u><br>register A. The result is stored in register A |

| ANL A, #data        | A (ANDed) data $\rightarrow$ A    | Immediate          | 2                  | ANL A, #10H  | The immediate data ANDed with the content<br>of register A. The result is stored in register A                                                     |

| ANL direct.A        | $A(ANDed)addr \rightarrow addr$   | Direct             | 2                  | ANL 20H,A    | The content of memory location 20H ANDed<br>with content of register A. The result is<br>stored at memory location 20H                             |

| ANL<br>direct.#data | A(ANDed)data →addr                | Immediate          | 3                  | ANL 20H,#40H | The content of memory location 20H ANDed<br>with data 40H. The result is stored at memory<br>location 20H                                          |

| ORL A, Rn           | A( <u>ORed)Rn</u> → A             | Register           | 1                  | ORL A, R4    | The content of register R4 is ORed with the<br>content of register A. The result is stored in<br>register A                                        |

| ORL A, direct       | A( <u>ORed)addr</u> → A           | Direct             | 2                  | ORL A, 20H   | The content of memory location 20H ORed<br>with content of register A. The result is<br>stored in register A                                       |

| ORL A, @Rn          | A (ORed)addr(Rn) $\rightarrow$ A       | Indirect  | 1 | ORL A, @R5   | The content of memory location whose address<br>is stored in R5 <u>ORed</u> with the content of<br>register A. The result is stored in register A |

|---------------------|----------------------------------------|-----------|---|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ORL A, #data        | A (ORed) data → A                      | Immediate | 2 | ORL A, #10H  | The immediate data 10H<br>content of register A. The result is stored in<br>register A                                                            |

| ORL direct A        | A( <u>ORed</u> )addr → addr            | Direct    | 2 | ORL 20H,A    | The content of memory location 20H ORed<br>with content of register A. The result is<br>stored at memory location 20H                             |

| ORL<br>direct.#data | A( <u>ORed</u> )data <del>→a</del> ddr | Immediate | 3 | ORL 20H,#40H | The content of memory location 20H ORed<br>with data 40H. The result is stored at memory<br>location 20H                                          |

| XRL A, Rn           | A( <u>XORed)Rn</u> → A                 | Register  | 1 | XRL A, R4    | The content of register R4 is XORed with the<br>content of register A. The result is stored in<br>register A                                      |

| XRL A, direct       | $A(XORed)addr \rightarrow A$           | Direct    | 2 | XRL A, 20H   | The content of memory location 20H XORed<br>with content of register A. The result is<br>stored in register A                                     |

| XRL A, @Rn          | A (XORed)addr(Rn)→A                    | Indirect  | 1 | XRL A, @R5   | The content of memory location whose address<br>is stored in R5 XORed with the content of<br>register A. The result is stored in register A       |

| XRL A, #data        | A (XORed) data → A                     | Immediate | 2 | XRL A, #10H  | The immediate data 10H XORed with the content of register A. The result is stored in register A                                                   |

|                     |                                        |           |   |              |                                                                                                                                                   |

| XRL direct A        | A(XORed)addr → addr                                                                                                          | Direct               | 2 | XRL 20H,A    | The content of memory location 20H XORed<br>with content of register A. The result is<br>stored at memory location 20H |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|---|--------------|------------------------------------------------------------------------------------------------------------------------|

| XRL<br>direct,#data | A(XORed)data → addr                                                                                                          | Immediate            | 3 | XRL 20H,#40H | The content of memory location 20H XORed<br>with data 40H. The result is stored at memory<br>location 20H              |

| CLR A               | A=0                                                                                                                          | Register<br>specific | 1 | CLR A        | This instruction clears the content of register A                                                                      |

| CPL A               | A=Ā                                                                                                                          | Register<br>specific | 1 | CPL A        | This instruction will compliments the content of register A                                                            |

| RL A                | $A_{n+l}=A_n$                                                                                                                | Register<br>specific | 1 | RL A         | This instruction will shift the content of register<br>A to left by one bit                                            |

| RLC A               | $\begin{array}{c} A_{n+1} \longrightarrow A_n \\ A_0 \longrightarrow CY \\ A_7 \longrightarrow CY \end{array}$               | Register<br>specific | 1 | RL A         | This instruction will shift the content of register<br>A to left by one bit through carry.                             |

| RR A                | $A_n \longrightarrow A_{n+1}$                                                                                                | Register<br>specific | 1 | RL A         | This instruction will shift the content of register<br>A to left by one bit                                            |

| RLC A               | $\begin{array}{ccc} A_n & \longrightarrow & A_{n+1} \\ CY & \longrightarrow & A_0 \\ CY & \longrightarrow & A_7 \end{array}$ | Register<br>specific | 1 | RL A         | This instruction will shift the content of register<br>A to left by one bit through carry.                             |

| SWAP A              | A(0-3) 🔁 A(4-7)                                                                                                              | Register<br>specific | 1 | SWAP A       | This instruction exchange the lower nibble and<br>higher nibble of register A                                          |

# **4. Bit Manipulation Instructions**

## 2.5. Bit Manipulation Instructions

| Mnemonic         | Operation                    | Addressing mode                              | Number of<br>Bytes | Example     | Description                                                                                                                                          |

|------------------|------------------------------|----------------------------------------------|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR Bit          | Bit=0                        | Register/ direct if<br>operated on carry bit | 1or 2              | CLR P2.3    | Clear the bit P2.3                                                                                                                                   |

| SETB Bit         | Bit=1                        | Register/ direct if<br>operated on carry bit | 1or 2              | SETB P1.0   | Set the bit P1.0                                                                                                                                     |

| CPL Bit          | Bit= <del>Bit</del>          | Register/ direct if<br>operated on carry bit | 1 or 2             | CPL 3.1     | Compliment the bit P3.1                                                                                                                              |

| ANL <u>C.Bit</u> | CY(ANDed)Bit → CY            | Direct                                       | 2                  | ANL C,ACC.3 | This instruction will perform logically<br>ANDing of carry bit and the bit<br>specified within instruction. The result<br>is stored in the carry bit |

| ORL <u>C,Bit</u> | $CY(ORed)Bit \rightarrow CY$ | Direct                                       | 2                  | ORL C,ACC.7 | This instruction will perform logically<br>ORing of carry bit and the bit specified<br>within instruction. The result is stored in<br>the carry bit  |

| MOV Bit.C        | CY → Bit                     | Direct                                       | 2                  | MOV ACC.2,C | The carry bit is copied on register A bit<br>number two                                                                                              |

| MOV C.Bit        | Bit $\rightarrow$ CY         | Direct                                       | 2                  | MOV C,ACC.1 | The register A bit number 1 copied to the carry bit                                                                                                  |

|                     | Single bit Jump Instructions |                    |                |                    |                                       |

|---------------------|------------------------------|--------------------|----------------|--------------------|---------------------------------------|

| Mnemonics           | operation                    | addressing<br>mode | No.of<br>bytes | Example            | Description                           |

| JB bit, rel address | jump to<br>target            | Direct             | 3              | JB P1.5, HERE      | jump if bit P1.5 is set               |

| JNB bit,rel address | jump to<br>target            | Direct             | 3              | JNB ACC.0,<br>NEXT | jump if bit ACC.0 not set             |

| JBC DIL rel address | jump to<br>target            | Direct             | 1              |                    | jump if bit ACC.7is set and clear bit |

| JC, rel address     | jump to<br>target            | Direct             | 3              | JC NEXT            | Jump if Carry is set                  |

| JNC, rel address    | jump to<br>target            | Direct             | 3              | JNC NEXT           | Jump if Carry not set                 |

#### BOOLEAN VARIABLE MANIPULATION

| CLR  | С       | Clear carry                             | 1 | 12 |

|------|---------|-----------------------------------------|---|----|

| CLR  | bit     | Clear direct bit                        | 2 | 12 |

| SETB | С       | Set carry                               | 1 | 12 |

| SETB | bit     | Set direct bit                          | 2 | 12 |

| CPL  | С       | Complement carry                        | 1 | 12 |

| CPL  | bit     | Complement direct bit                   | 2 | 12 |

| ANL  | C,bit   | AND direct bit to carry                 | 2 | 24 |

| ANL  | C,/bit  | AND complement of direct bit to carry   | 2 | 24 |

| ORL  | C,bit   | OR direct bit to carry                  | 2 | 24 |

| ORL  | C,/bit  | OR complement of direct bit to carry    | 2 | 24 |

| MOV  | C,bit   | Move direct bit to carry                | 2 | 12 |

| MOV  | bit,C   | Move carry to direct bit                | 2 | 24 |

| JC   | rel     | Jump if carry is set                    | 2 | 24 |

| JNC  | rel     | Jump if carry not set                   | 2 | 24 |

| JB   | rel     | Jump if direct bit is set               | 3 | 24 |

| JNB  | rel     | Jump if direct bit is not set           | 3 | 24 |

| JBC  | bit,rel | Jump if direct bit is set and clear bit | 3 | 24 |

# **5. Program Branching Instructions:**

Branching instructions are classified into the two groups:

- 1. Jump instructions

- 2. Subroutine instructions

Jump instructions a. Short relative jump b. Absolute jump c. Long jump

### Short relative jump

| J F -       |                                                               |                  |  |

|-------------|---------------------------------------------------------------|------------------|--|

| Instruction | Description Conditions for jump                               |                  |  |

| SJMP        | Unconditional short jump e.g. SJMP here -                     |                  |  |

| JC          | Jump if carry e.g JC here                                     | CY=1             |  |

| JNC         | Jump if not carry e.g JNC here                                | CY=0             |  |

| JZ          | Jump if zero e.g JZ here                                      | A=0              |  |

| JNZ         | Jump if not zero JBC P1.5, here                               | A≠0              |  |

| JB          | Jump if bit e.g JB P1.5, here                                 | Bit =1           |  |

| JNB         | Jump if not bit e.g JNB P1.5, here                            | Bit=0            |  |

| JBC         | Jump if bit and clear the bit e.g JBC P1.5, here              | Bit=1            |  |

| CJNE        | compares the first two operands and jumps to the specified    | SFR or direct or |  |

|             | destination if their values are not equal. If the values are  | indirect address |  |

|             | the same, execution continues next instruction. becomes equal |                  |  |

|             | e.g. CJNE A,#25H, here                                        |                  |  |

| DJNZ        | decrements the byte indicated by the first operand and, if    | SFR or immediate |  |

|             | the resulting value is not zero, jumps to the address         |                  |  |

|             | specified in the second operand.                              | indirect address |  |

|             |                                                               |                  |  |

|             | e.g. DJNZ R0, here                                            | becomes zero     |  |

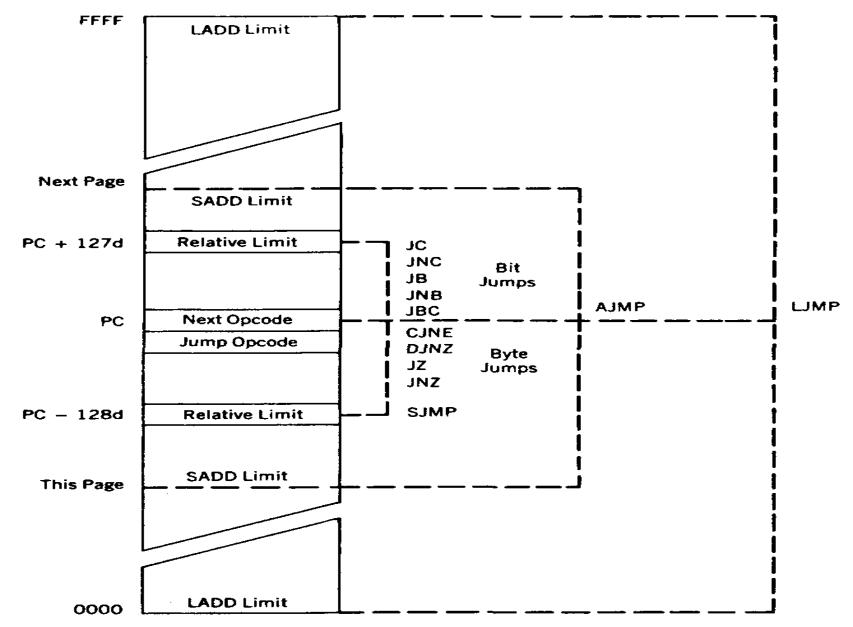

#### Absolute jump: AJMP <11 bit address>

The Absolute jump is two byte unconditional jump. It jumps within page of 2K byte. In 8051, 64 Kbyte of program memory space is divided into 32 pages of 2Kbyte each.

#### Long Jump : (long jump) LJMP <16 bit address>

It is used to access the entire program memory from 0000H to FFFFH. It is a 3-byte instruction (except for JMP @ A+DPTR). First byte is the op-code and second and third bytes represent the 16-bit target address which is any memory location from 0000 to FFFFH. eg: LJMP 7000H

#### **Subroutine Instructions**

In the 8051 a subroutines are handled by CALL and RET instructions. The main difference between CALL and JUMP instructions is that CALL has return path and jump has no return path. When CALL instructions are executed then the content of the PC pointed to the next of the CALL is stored into the stack pointer. During RET instructions it is loaded into the PC.

There are two types of CALL instructions

- a. Absolute call : ACALL

- b. Long call : LCALL

#### Absolute call

#### ACALL <11 bit address>

The Absolute CALL is two byte call instruction. It call within page of 2K byte. In 8051, 64 Kbyte of program memory space is divided into 32 pages of 2Kbyte each.

#### Long CALL

#### LCALL <16 bit address>

This is long call instruction which unconditionally calls the subroutine located at the indicated 16 bit address. This is a 3 byte instruction. No flags are affected. e.g. LCALL 7000H

#### **RET instruction**

A RET instruction pops top two content from the stack memory and loaded into PC. After execution of RET instruction a main program is executed. e.g. RET

Jump on bit conditions Compare bytes and jump if *not* equal Decrement byte and jump if zero Jump unconditionally Call a subroutine Return from a subroutine

#### Jump Instruction Ranges

#### Memory Address (HEX)

# **Bit Jumps**

## Mnemonic Operation

JC raddJump relative if the carry flag is set to 1JNC raddJump relative if the carry flag is reset to 0JB b,raddJump relative if addressable bit is set to 1JNB b,raddJump relative if addressable bit is reset to 0JBC b,raddJump relative if addressable bit is set, and clear the addressable bit to 0

| ADDRESS | MNEMONIC   | COMMENT                                                                              |

|---------|------------|--------------------------------------------------------------------------------------|

| LOOP:   | MOV A,#10h | ;A = 10h                                                                             |

|         | MOV RO,A   | ; R0 = 10h                                                                           |

| ADDA :  | ADD A,RO   | ;add RO to A                                                                         |

|         | JNC ADDA   | ; if the carry flag is 0, then no carry is                                           |

|         |            | ; <i>true</i> ; jump to address ADDA; jump until A<br>; is FOh; the C flag is set to |

|         |            | <b>U</b>                                                                             |

|         |            | ;1 on the next ADD and no carry is                                                   |

; false; do the next instruction

## **Byte Jumps**

### Operation

Mnemonic

| CJNE A, add, radd | Compare the contents of the A register with the contents of the direct address; if they are <i>not</i> equal, then jump to the relative address; set the carry flag to 1 if A is less than the contents of the direct address; otherwise, set the carry flag to 0                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CJNE A, #n, radd  | Compare the contents of the A register with the immediate<br>number n; if they are <i>not</i> equal, then jump to the relative<br>address; set the carry flag to 1 if A is less than the number;<br>otherwise, set the carry flag to 0                                               |

| CJNE Rn,#n,radd   | Compare the contents of register Rn with the immediate<br>number n; if they are <i>not</i> equal, then jump to the relative<br>address; set the carry flag to 1 if Rn is less than the number;<br>otherwise, set the carry flag to 0                                                 |

| CJNE @Rp,#n,radd  | Compare the contents of the address contained in register Rp<br>to the number n; if they are <i>not</i> equal, then jump to the<br>relative address; set the carry flag to 1 if the contents of the<br>address in Rp are less than the number; otherwise, set the<br>carry flag to 0 |

| DJNZ Rn,radd  | Decrement register Rn by 1 and jump to the relative address if<br>the result is <i>not</i> zero; no flags are affected                                             |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DJNZ add,radd | Decrement the direct address by 1 and jump to the relative<br>address if the result is <i>not</i> 0; no flags are affected unless the<br>direct address is the PSW |

| JZ radd       | Jump to the relative address if A is 0; the flags and the A register are not changed                                                                               |

| JNZ radd      | Jump to the relative address if A is <i>not</i> 0; the flags and the A register are not changed                                                                    |

## **Unconditional Jumps**

| Mnemonic    | Operation                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JMP @A+DPTR | Jump to the address formed by adding A to the DPTR; this is an<br>unconditional jump and will always be done; the address can<br>be anywhere in program memory; A, the DPTR, and the flags<br>are unchanged |

| AJMP sadd   | Jump to absolute short range address sadd; this is an unconditional jump and is always taken; no flags are affected                                                                                         |

| LJMP ladd   | Jump to absolute long range address ladd; this is an unconditional jump and is always taken; no flags are affected                                                                                          |

| SJMP radd   | Jump to relative address radd; this is an unconditional jump and is always taken; no flags are affected                                                                                                     |

| NOP         | Do nothing and go to the next instruction; NOP (no operation) is<br>used to waste time in a software timing loop; or to leave room<br>in a program for later additions; no flags are affected               |

# **Calls and Returns**

## Mnemonic Operation

- ACALL sadd Call the subroutine located on the same page as the address of the opcode immediately following the ACALL instruction; push the address of the instruction immediately after the call on the stack

- LCALL ladd Call the subroutine located anywhere in program memory space; push the address of the instruction immediately following the call on the stack

- RET Pop two bytes from the stack into the program counter

- RETI Pop two bytes from the stack into the program counter and reset the interrupt enable flip-flops

#### 8051 conditional jump instructions

| Instructions   | Actions                          |

|----------------|----------------------------------|

| JZ             | Jump if $A = 0$                  |

| JNZ            | Jump if A $\neq$ 0               |

| DJNZ           | Decrement and Jump if A $\neq$ 0 |

| CJNE A,byte    | Jump if A $\neq$ byte            |

| CJNE reg,#data | Jump if byte $\neq$ #data        |

| JC             | Jump if $CY = 1$                 |

| JNC            | Jump if $CY = 0$                 |

| JB             | Jump if bit $= 1$                |

| JNB            | Jump if bit $= 0$                |

| JBC            | Jump if bit $=$ 1 and clear bit  |

## All conditional jumps are short jumps

The address of the target must within -128 to +127 bytes of the contents of PC

| Mnemonic          | Operation                                                                                         | of Bytes |      | Example     | Description                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------|----------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACALL 11 bit addr | PC=PC+2<br>SP=SP+1<br>SP=PC <sub>0-7</sub><br>SP=SP+1<br>SP=PC <sub>8-15</sub><br>PC=11 bit addr  | 2        | 2KB  | ACALL DELAY | <ol> <li>program counter is incremented by<br/>two</li> <li>stack pointer is incremented by one</li> <li>lower byte of the stack pointer is<br/>pushed on the SP</li> <li>stack pointer incremented by one<br/>and the higher byte is pushed on the<br/>stack</li> <li>program counter is loaded with 11<br/>bit address</li> </ol> |

| LCALL 16 bit addr | PC=PC+3<br>SP=SP+1<br>SP=PC <sub>0-7</sub><br>SP=SP+1<br>SP=PC <sub>8-15</sub><br>PC= 16 bit addr | 3        | 64KB | LCALL LCD   | <ol> <li>program counter is incremented by<br/>two</li> <li>stack pointer is incremented by one</li> <li>lower byte of the stack pointer is<br/>pushed on the SP</li> <li>stack pointer incremented by one<br/>and the higher byte is pushed on the<br/>stack</li> <li>program counter is loaded with 16<br/>bit address</li> </ol> |

| RET               | PC <sub>8-15</sub> =SP<br>SP=SP-1<br>PC <sub>0-7</sub> = SP<br>SP=SP-1                            | 1        |      | RET         | <ol> <li>the higher byte is pop out of the<br/>stack</li> <li>stack pointer is decremented by one</li> <li>lower byte is pop out of the stack<br/>pointer</li> <li>stack pointer is decremented by one</li> <li>5.</li> </ol>                                                                                                       |